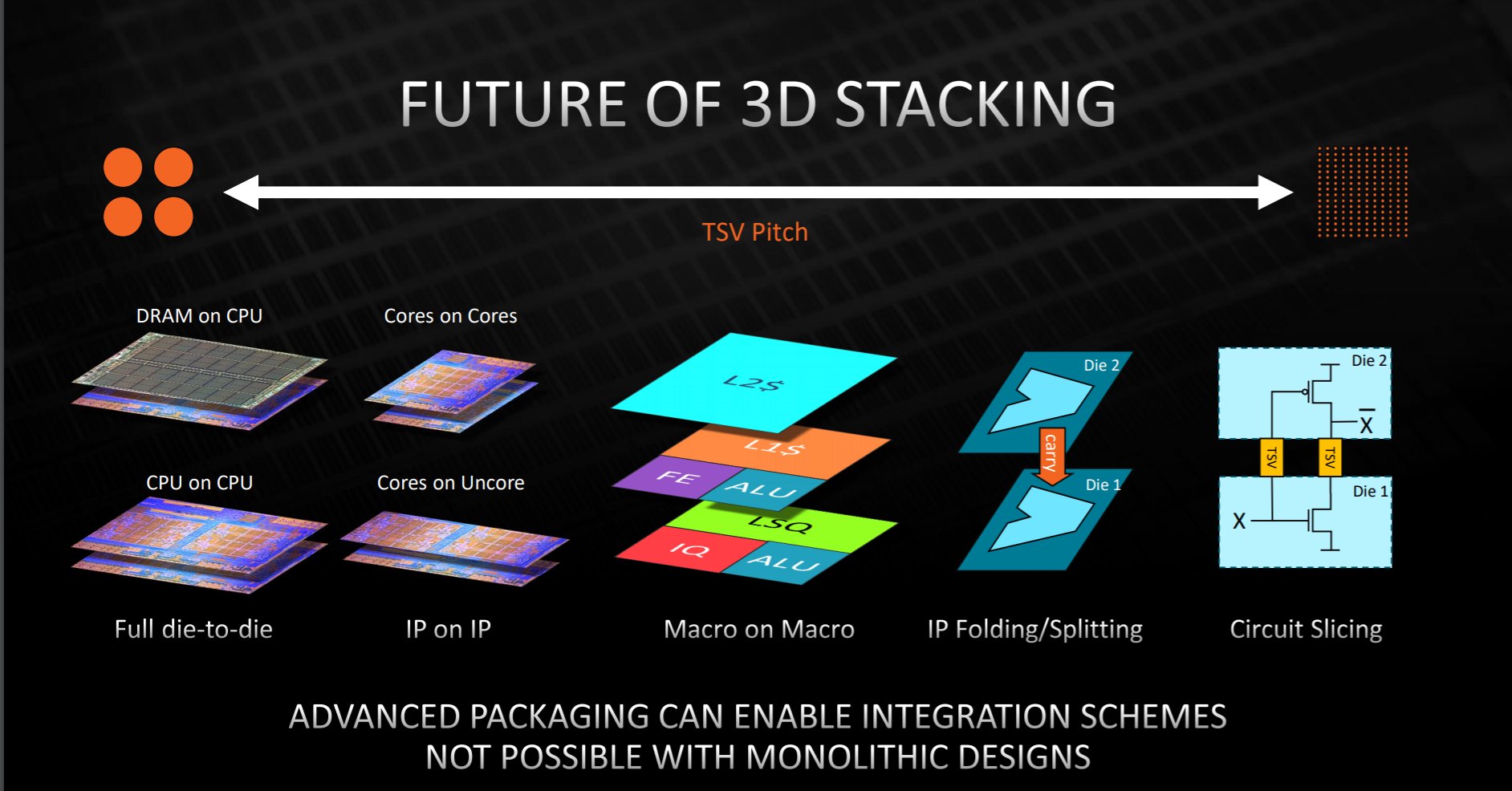

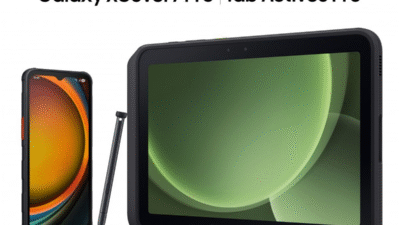

3D Chip Stacking: Mendorong Batas Kinerja dan Densitas dalam Desain Mikroelektronik

Dalam era komputasi yang serba cepat dan permintaan yang terus meningkat untuk perangkat elektronik yang lebih kecil, lebih cepat, dan lebih efisien, industri mikroelektronik terus mencari cara inovatif untuk meningkatkan kinerja dan kemampuan perangkat. Salah satu teknologi yang menjanjikan yang telah muncul dalam beberapa tahun terakhir adalah 3D chip stacking, juga dikenal sebagai integrasi 3D. 3D chip stacking melibatkan penumpukan beberapa lapisan wafer silikon atau die dan saling menghubungkannya secara vertikal untuk membuat sirkuit terintegrasi (IC) tiga dimensi. Pendekatan ini menawarkan beberapa keuntungan dibandingkan desain 2D tradisional, termasuk peningkatan kinerja, pengurangan ukuran, konsumsi daya yang lebih rendah, dan peningkatan fungsionalitas.

Prinsip dan Teknik

3D chip stacking dibangun di atas prinsip mengintegrasikan beberapa die aktif atau pasif dalam susunan vertikal dan menghubungkannya menggunakan berbagai teknik interkoneksi. Prosesnya biasanya melibatkan langkah-langkah utama berikut:

- Fabrikasi Die: Langkah pertama adalah memfabrikasi die individual pada wafer silikon menggunakan proses manufaktur semikonduktor standar. Die ini dapat berisi berbagai komponen fungsional, seperti unit pemrosesan, memori, sensor, atau sirkuit campuran-sinyal.

- Penipisan Wafer: Setelah fabrikasi die, wafer ditipiskan hingga ketebalan yang diinginkan menggunakan teknik seperti penggilingan balik atau pengetsaan kimia. Penipisan wafer mengurangi jejak vertikal susunan yang ditumpuk dan memfasilitasi interkoneksi yang lebih baik.

Bonding dan Penumpukan Die: Wafer atau die yang ditipiskan kemudian diikat dan ditumpuk satu sama lain menggunakan berbagai teknik bonding. Beberapa metode bonding umum meliputi:

- Die-to-Wafer Bonding: Dalam pendekatan ini, die individual diikat ke wafer pembawa menggunakan perekat atau bonding logam. Wafer pembawa memberikan dukungan mekanis dan memfasilitasi penanganan selama proses penumpukan.

- Wafer-to-Wafer Bonding: Wafer yang lengkap diikat langsung satu sama lain menggunakan bonding logam atau oksida. Metode ini cocok untuk membuat tumpukan memori atau struktur 3D lainnya yang memerlukan kerapatan interkoneksi yang tinggi.

- Bonding Termokompresi: Bonding termokompresi melibatkan penerapan panas dan tekanan untuk membentuk ikatan metalurgi antara permukaan yang diikat. Teknik ini biasanya digunakan untuk bonding tembaga-ke-tembaga atau bonding logam-ke-logam lainnya.

- Via Through-Silicon (TSV): TSV adalah lubang vertikal yang menembus die silikon, menyediakan jalur listrik antara lapisan yang ditumpuk. TSV difabrikasi menggunakan teknik pengetsaan dan deposisi, dan biasanya diisi dengan logam konduktif, seperti tembaga atau tungsten. TSV memainkan peran penting dalam mengaktifkan interkoneksi kepadatan tinggi dan kinerja tinggi dalam susunan 3D.

- Interkoneksi dan Pengemasan: Setelah penumpukan dan TSV, lapisan yang ditumpuk saling terhubung menggunakan berbagai teknik interkoneksi, seperti bonding microbump, bonding kawat, atau redistribusi wafer. Susunan yang ditumpuk kemudian dikemas menggunakan teknik pengemasan standar untuk memberikan perlindungan dan memfasilitasi pemasangan ke sistem yang lebih besar.

Keuntungan dari 3D Chip Stacking

3D chip stacking menawarkan beberapa keuntungan dibandingkan desain 2D tradisional, menjadikannya teknologi yang menarik untuk berbagai aplikasi:

- Peningkatan Kinerja: 3D chip stacking mengurangi panjang interkoneksi dan latensi antara komponen, yang menghasilkan peningkatan kinerja dan kecepatan yang signifikan. Jalur yang lebih pendek memungkinkan sinyal untuk melakukan perjalanan lebih cepat, mengurangi penundaan sinyal dan meningkatkan kinerja sistem secara keseluruhan.

- Pengurangan Ukuran: Dengan menumpuk beberapa die secara vertikal, 3D chip stacking memungkinkan untuk membuat perangkat yang lebih kecil dan lebih ringkas. Hal ini sangat bermanfaat untuk aplikasi di mana ruang terbatas, seperti ponsel pintar, perangkat yang dapat dikenakan, dan implan medis.

- Konsumsi Daya yang Lebih Rendah: Panjang interkoneksi yang lebih pendek dalam susunan 3D juga menghasilkan konsumsi daya yang lebih rendah. Jalur yang lebih pendek berarti lebih sedikit resistansi dan kapasitansi, yang mengurangi daya yang dibutuhkan untuk mengirimkan sinyal. Selain itu, 3D chip stacking memungkinkan untuk penempatan yang lebih efisien dari komponen, yang selanjutnya dapat mengoptimalkan konsumsi daya.

- Peningkatan Fungsionalitas: 3D chip stacking memungkinkan integrasi dari berbagai die dengan fungsi yang berbeda dalam satu paket. Hal ini membuka kemungkinan untuk membuat sistem yang lebih kompleks dan multifungsi. Misalnya, susunan 3D dapat mengintegrasikan prosesor, memori, dan sensor, yang memungkinkan untuk membuat sistem-dalam-paket (SiP) yang sangat terintegrasi.

- Bandwidth Memori yang Lebih Tinggi: 3D chip stacking sangat bermanfaat untuk aplikasi memori, di mana dapat menyediakan bandwidth memori yang jauh lebih tinggi dibandingkan solusi memori tradisional. Dengan menumpuk chip memori dan menghubungkannya menggunakan TSV, 3D chip stacking memungkinkan untuk transfer data paralel yang lebih cepat dan peningkatan kinerja memori.

Aplikasi 3D Chip Stacking

3D chip stacking menemukan aplikasi di berbagai bidang, termasuk:

- Ponsel Pintar dan Perangkat Seluler: 3D chip stacking digunakan untuk membuat ponsel pintar dan perangkat seluler yang lebih kecil, lebih cepat, dan lebih efisien daya. Ini memungkinkan integrasi prosesor, memori, dan komponen lain dalam satu paket, mengurangi ukuran dan meningkatkan kinerja.

- Komputasi Kinerja Tinggi: 3D chip stacking digunakan dalam sistem komputasi kinerja tinggi (HPC) untuk meningkatkan kinerja dan mengurangi konsumsi daya. Ini memungkinkan integrasi prosesor, memori, dan komponen lain dengan bandwidth tinggi dan latensi rendah, menghasilkan kinerja komputasi yang lebih cepat.

- Grafis dan Game: 3D chip stacking digunakan dalam kartu grafis dan konsol game untuk meningkatkan kinerja grafis dan memori. Ini memungkinkan integrasi chip memori bandwidth tinggi dengan GPU, memberikan tekstur dan resolusi yang lebih cepat dan lebih halus.

- Kecerdasan Buatan: 3D chip stacking digunakan dalam aplikasi kecerdasan buatan (AI) untuk meningkatkan kinerja dan efisiensi sistem AI. Ini memungkinkan integrasi prosesor, memori, dan komponen lain dengan bandwidth tinggi dan latensi rendah, menghasilkan pelatihan dan inferensi model AI yang lebih cepat.

- Medis dan Kesehatan: 3D chip stacking digunakan dalam perangkat medis dan aplikasi perawatan kesehatan untuk membuat perangkat yang lebih kecil, lebih kuat, dan lebih efisien daya. Ini memungkinkan integrasi sensor, prosesor, dan komponen lain dalam satu paket, yang memungkinkan untuk membuat perangkat yang dapat dikenakan, implan, dan perangkat diagnostik yang canggih.

Tantangan dan Tren Masa Depan

Meskipun 3D chip stacking menawarkan banyak keuntungan, juga menghadirkan beberapa tantangan:

- Manajemen Termal: Menumpuk beberapa die dapat menghasilkan masalah manajemen termal, karena panas yang dihasilkan oleh die dapat menyebabkan masalah kinerja dan keandalan. Solusi manajemen termal yang efektif, seperti pendinginan cair atau spread termal, diperlukan untuk menghilangkan panas secara efisien dari susunan 3D.

- Yield dan Keandalan: Proses manufaktur 3D chip stacking lebih kompleks daripada proses manufaktur 2D, yang dapat menyebabkan yield dan masalah keandalan. Tindakan kontrol kualitas dan inspeksi yang ketat diperlukan untuk memastikan bahwa susunan 3D diproduksi dengan yield dan keandalan yang tinggi.

- Biaya: Biaya manufaktur 3D chip stacking saat ini lebih tinggi daripada biaya manufaktur 2D. Seiring dengan kemajuan teknologi dan volume produksi meningkat, biaya diharapkan menurun, membuat 3D chip stacking lebih kompetitif untuk berbagai aplikasi.

- Desain dan Alat: Desain dan alat untuk 3D chip stacking masih berkembang. Alat desain yang lebih canggih dan metodologi diperlukan untuk mengoptimalkan desain, mensimulasikan kinerja, dan memverifikasi fungsionalitas susunan 3D.

Tren masa depan dalam 3D chip stacking meliputi:

- Interkoneksi Kepadatan Tinggi: Penelitian dan pengembangan terus berfokus pada pengembangan interkoneksi kepadatan tinggi, seperti TSV dan microbump, untuk meningkatkan kinerja dan fungsionalitas susunan 3D.

- Heterogeneous Integration: 3D chip stacking memungkinkan integrasi die yang berbeda dengan fungsi yang berbeda, yang mengarah pada pengembangan sistem yang lebih kompleks dan multifungsi.

- Material Baru: Material baru, seperti graphene dan nanokawat, dieksplorasi untuk digunakan dalam 3D chip stacking untuk meningkatkan kinerja, mengurangi konsumsi daya, dan meningkatkan keandalan.

- Teknik Manufaktur Tingkat Lanjut: Teknik manufaktur tingkat lanjut, seperti fabrikasi aditif dan perakitan otomatis, sedang dikembangkan untuk mengurangi biaya dan meningkatkan yield 3D chip stacking.

Kesimpulan

3D chip stacking adalah teknologi yang menjanjikan yang menawarkan beberapa keuntungan dibandingkan desain 2D tradisional, termasuk peningkatan kinerja, pengurangan ukuran, konsumsi daya yang lebih rendah, dan peningkatan fungsionalitas. Ia menemukan aplikasi di berbagai bidang, termasuk ponsel pintar, komputasi kinerja tinggi, grafis, kecerdasan buatan, medis, dan perawatan kesehatan. Meskipun 3D chip stacking menghadirkan beberapa tantangan, penelitian dan pengembangan yang sedang berlangsung mengatasi tantangan ini dan membuka jalan untuk inovasi masa depan. Saat teknologi terus maju, 3D chip stacking siap untuk memainkan peran yang semakin penting dalam mendorong batas kinerja dan densitas dalam desain mikroelektronik, yang memungkinkan untuk pengembangan perangkat elektronik yang lebih kecil, lebih cepat, dan lebih efisien.